Comme j’ai eu l’occasion de l’écrire dans un précédent billet, le choix des solutions de mémoire flash repose sur des critères technologiques et sur la manière dont est gérée la mémoire flash.

Dans son offre UCS Invicta , Cisco donne un rôle clé à son système d’exploitation (Cisco UCS Invicta OS) pour optimiser efficacement la mémoire flash. Reprenons quelques fonctions déterminantes dans le fonctionnement d’un système à mémoire flash :

Facteur d’amplification d’écriture :

L’amplification est la conséquence du déplacement des données pour effacer l’intégralité des blocs flash sous-utilisés. Cela a pour effet de consommer de l’espace excédentaire et de réduire la longévité des mémoires flash en exigeant des opérations d’écriture inutiles.

Dans la majorité des cas on observe sur les produits du marché des amplifications d’écriture de 10 :1 (qui peut atteindre 40 :1 pour certaines solutions).

En écrivant dans la mémoire flash avec des blocs de longueur fixes (non aléatoire) et complets l’OS Invicta réduit le facteur d’ amplification d’écriture (1,1 :1 à 1,3 :1). On peut ainsi obtenir une longévité 8 à 10 fois supérieure pour les mêmes composants utilisés dans un système géré différemment.

Déduplication des données à haute vitesse :

La déduplication a pour effet de diminuer le nombre d’écriture et d’obtenir ainsi une meilleure endurance des composants flash. Lorsque la déduplication est activée dans UCS Invicta , elle s’effectue à la volée pour 100 % des écritures entrantes. Un algorithme de hachage de blocs fixes hache chaque opération d’écriture en 4 Ko, puis la compare à des blocs existants en mémoire. Si une correspondance est trouvée, les données sont lues pour vérifier la duplication, et un pointeur est stocké plutôt qu’un doublon des données.

Détection et correction d’erreur :

La détection d’erreur utilise le même algorithme de hachage que la déduplication. Toutes les opérations d’écriture entrantes sont hachées et stockées dans une table de hachage. Lors de la relecture avec la détection d’erreur activée, l’OS Invicta détermine si les bits sont ceux qui ont été stockés sur les cellules flash. Si une erreur est détectée, les données Initiales peuvent être récupérées. Les informations de hachage et les métadonnées sont enregistrées à la fois dans la mémoire du système et sur les Flashs.

L’intégrité des données en cas de coupure de courant :

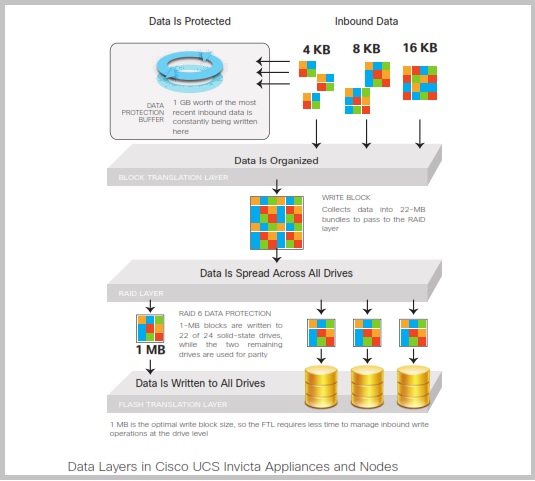

L’’intégrité des données dans un système UCS Invicta, en cas de perte d’alimentation électrique, est garantie par un buffer de protection de 1Go, par nœud et par appliance, pour les opérations d’écriture entrantes qui n’ont pas été encore écrites dans la mémoire flash. Le tampon est alimenté par des super condensateurs et, après retour de l’alimentation, les données sont relues dans le buffer et la validation peut ainsi se terminer en assurant l’intégrité des données.

Pour information l’offre Cisco UCS Invicta se décline sous deux formes :